# basic education

Department: Basic Education **REPUBLIC OF SOUTH AFRICA**

NATIONAL SENIOR CERTIFICATE

**GRADE 12**

# **ELECTRICAL TECHNOLOGY: DIGITAL**

----

**NOVEMBER 2021**

**MARKING GUIDELINES**

-----

**MARKS: 200**

These marking guidelines consist of 16 pages.

Please turn over

#### INSTRUCTIONS TO THE MARKERS

- 1. All questions with multiple answers imply that any relevant, acceptable answer should be considered.

- 2. Calculations:

- 2.1 All calculations must show the formulae.

- 2.2 Substitution of values must be done correctly.

- 2.3 All answers MUST contain the correct unit to be considered.

- 2.4 Alternative methods must be considered, provided that the correct answer is obtained.

- 2.5 Where an incorrect answer could be carried over to the next step, the first answer will be deemed incorrect. However, should the incorrect answer be carried over correctly, the marker has to recalculate the values, using the incorrect answer from the first calculation. If correctly used, the candidate should receive the full marks for subsequent calculations.

- 3. These marking guidelines are only a guide with model answers. Alternative interpretations must be considered and marked on merit. However, this principle should be applied consistently throughout the marking session at ALL marking centres.

Electrical Technology: Digital

NSC – Marking Guidelines

DBE/November 2021

## **QUESTION 1: MULTIPLE-CHOICE QUESTIONS**

| 1.1  | C 🗸                        |                | (1)                |

|------|----------------------------|----------------|--------------------|

| 1.2  | В 🗸                        |                | (1)                |

| 1.3  | С 🗸                        |                | (1)                |

| 1.4  | в 🗸 (A will also be accept | ed as correct) | (1)                |

| 1.5  | С 🗸                        |                | (1)                |

| 1.6  | C 🗸                        |                | (1)                |

| 1.7  | D 🗸                        |                | (1)                |

| 1.8  | A 🗸                        |                | (1)                |

| 1.9  | C ✓                        |                | (1)                |

| 1.10 | A 🗸                        |                | (1)                |

| 1.11 | D 🗸                        | ÉcoleBooks     | (1)                |

| 1.12 | A 🗸                        |                | (1)                |

| 1.13 | C 🗸                        |                | (1)                |

| 1.14 | B 🗸                        |                | (1)                |

| 1.15 | D 🗸                        |                | (1)<br><b>[15]</b> |

(2)

(1)

(1) **[10]**

#### QUESTION 2: OCCUPATIONAL HEALTH AND SAFETY

- 2.1 To identify and communicate potential hazards ✓

- To identify potential major incidents ✓ at the workplace to the employer.

#### OR

- To review the effectiveness of health and safety measures.

- To investigate complaints by employees relating to health and safety at work. (2)

- 2.2 Your right to earn a living wage. ✓

- Your right to work for reasonable hours. ✓

- Your right to belong to a trade union.

- 2.3 An unsafe act is an action committed by a person which may lead to an accident or unsafe condition and/or loss. ✓ An unsafe condition is a work related environmental condition which may lead to or contribute to an accident and/or loss. ✓ (2)

- 4 High impact, low probability.

- High impact, high probability.

- Low impact, low probability.

- Low impact, high probability, ÉcoleBooks

- Qualitative risk analysis.

- Quantitative risk analysis.

- 2.5 'Danger' means anything that may cause injury to a person ✓ or damage to property. ✓ (2)

- Use an apron ✓ to protect your clothes from staining.

- Use protective glasses to protect your eyes.

- Use latex gloves to prevent skin irritation.

- Use a mask to reduce the risk of breathing fumes.

| Electrical Techno              | blogy: Digital 5 DBE/November 2021<br>NSC – Marking Guidelines                                                                                                                                                                                                                                                                                                     |     |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| QUESTION 3: SWITCHING CIRCUITS |                                                                                                                                                                                                                                                                                                                                                                    |     |  |  |  |  |  |

| 3.1 3.1.1                      | Resistor $R_1$ is a pull up $\checkmark$ resistor keeping pin 2 high and the circuit                                                                                                                                                                                                                                                                               |     |  |  |  |  |  |

|                                | in its stable state. ✓                                                                                                                                                                                                                                                                                                                                             | (2) |  |  |  |  |  |

| 3.1.2                          | 0 V 🗸                                                                                                                                                                                                                                                                                                                                                              | (1) |  |  |  |  |  |

| 3.1.3                          | LED will be ON 🗸                                                                                                                                                                                                                                                                                                                                                   | (1) |  |  |  |  |  |

| 3.1.4                          | ±6 V ✓<br>⅔V <sub>cc</sub>                                                                                                                                                                                                                                                                                                                                         | (1) |  |  |  |  |  |

| 3.1.5                          | The duration $\checkmark$ of the train of on-off pulses during switch bounce are shorter than the charging cycle of the capacitor. $\checkmark$ Only when the capacitor has charged to point Y will the circuit change state.                                                                                                                                      | (2) |  |  |  |  |  |

| 3.1.6                          | Bounce                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |  |  |

|                                | Input<br>V <sub>C1</sub>                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

|                                | Output t<br>t                                                                                                                                                                                                                                                                                                                                                      |     |  |  |  |  |  |

|                                | NOTE: 2 marks = 1 for each trigger point (the output must be a                                                                                                                                                                                                                                                                                                     |     |  |  |  |  |  |

|                                | square wave) 1 mark = correct orientation                                                                                                                                                                                                                                                                                                                          | (3) |  |  |  |  |  |

| 3.2 3.2.1                      | Bistable 🗸 multivibrator                                                                                                                                                                                                                                                                                                                                           | (1) |  |  |  |  |  |

| 3.2.2                          | $R_2$ provides feedback to the non-inverting input. 🗸                                                                                                                                                                                                                                                                                                              | (1) |  |  |  |  |  |

| 3.2.3                          | Positive 🗸                                                                                                                                                                                                                                                                                                                                                         | (1) |  |  |  |  |  |

| 3.2.4                          | <ul> <li>plates of the capacitor immediately rises to the magnitude of the input pulse. ✓</li> <li>This is fed to the inverting input of the Op-amp. ✓</li> <li>The Op-amp compares this voltage to the voltage at the non-inverting input and amplifies the difference. ✓</li> <li>Its output is driven to negative saturation where it will remain. ✓</li> </ul> | (4) |  |  |  |  |  |

Download more resources like this on ECOLEBOOKS.COM

- When a negative voltage is applied the inverting input is still smaller ✓ than the voltage on the non-inverting input keeping the output positive.

- The output will only change state when a voltage greater (positive) than the voltage on the non-inverting input is applied to the inverting input.

(2) (2)

3.3.2 The trigger voltage level is determined by the ratio of R<sub>1</sub> to (R<sub>1</sub>+R<sub>F</sub>)  $\checkmark$

Trigger voltage (V+)=

$$\frac{R_1}{R_1 + R_F} \times V_{out}$$

(1)

- 3.3.3 This circuit makes use of closed loop gain, ✓ because a portion of the output is fed back to the non-inverting input. ✓ (2)

- 3.3.4 Filters out unwanted noise from the input signal. ✓

Amplifies the input to a bigger output value. ✓

Changes the analogue input into a digital square wave. (2)

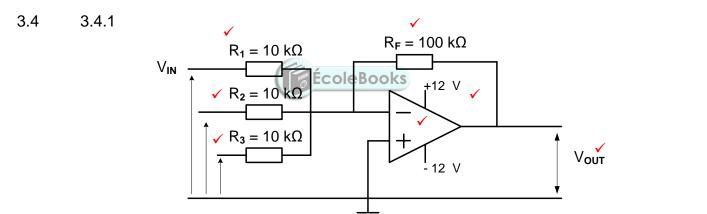

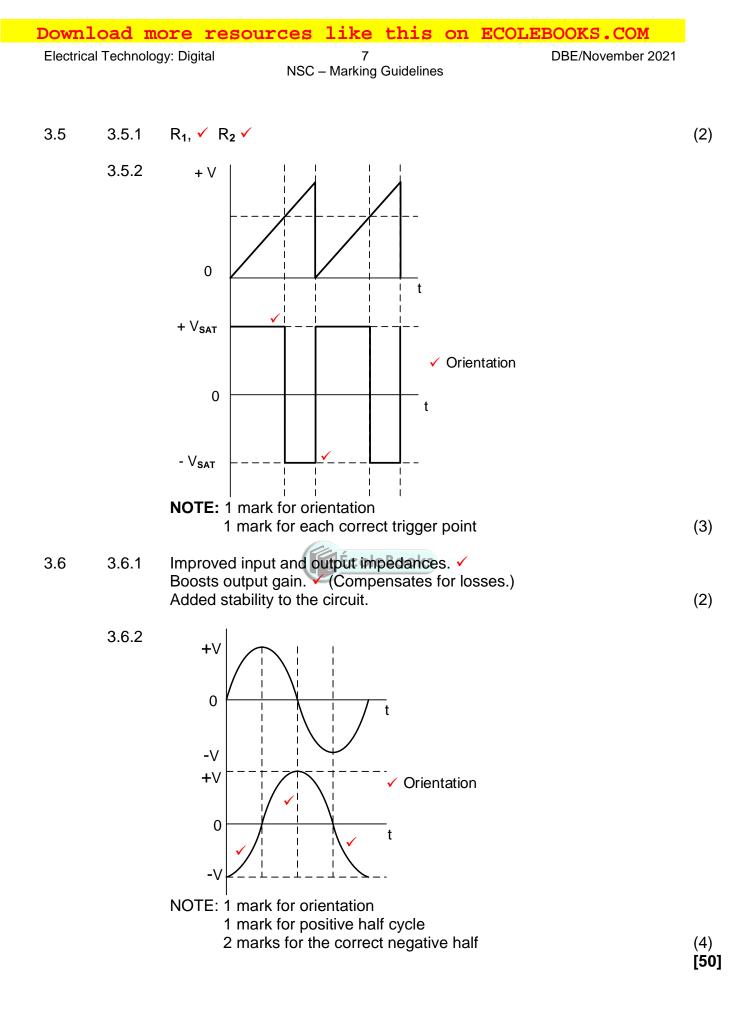

3.4.2

$$V_{OUT} = -\left(V_{1} \times \frac{R_{F}}{R_{1}} + V_{2} \times \frac{R_{F}}{R_{2}} + V_{3} \times \frac{R_{F}}{R_{3}}\right) \qquad \checkmark$$

$$= -\left(0.5 \times \frac{100 \times 10^{3}}{10 \times 10^{3}} + (-0.8) \times \frac{100 \times 10^{3}}{10 \times 10^{3}} + 0.2 \times \frac{100 \times 10^{3}}{10 \times 10^{3}}\right) \qquad \checkmark$$

$$= 1 V \qquad \checkmark \qquad (3)$$

3.4.3 The polarity of the output voltage will become negative because the sum of the voltages at the input is positive. ✓ This positive value is then inverted ✓ and amplified by the inverting summing amplifier and changed into a negative output. ✓

NOTE: If a learner correctly calculates the new output voltage and writes a concluding statement that the output changed to negative, 3 marks will be awarded. A calculation only, warrants 2 marks.

(3)

(7)

Copyright reserved

#### 8 NSC – Marking Guidelines

(1)

(3)

(1)

(2)

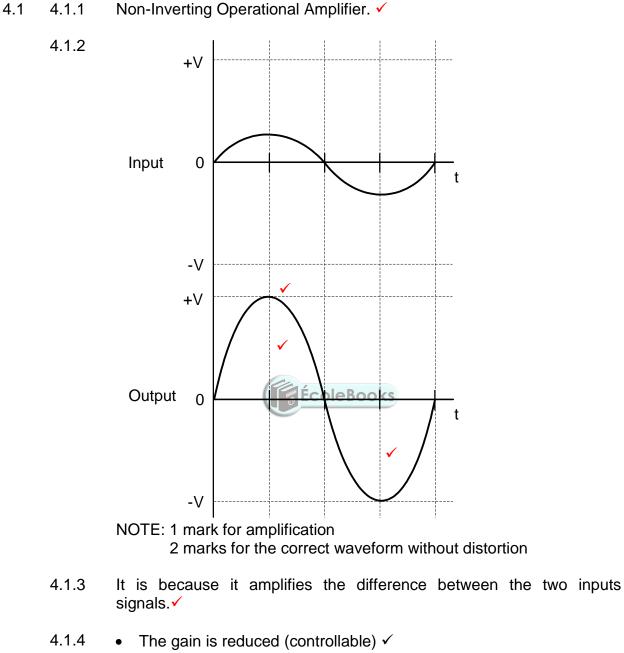

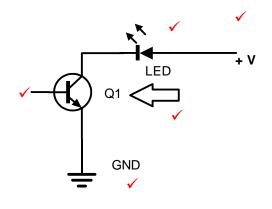

## **QUESTION 4: SEMICONDUCTOR DEVICES**

- It stabilises the amplifier ✓

- Distortion of the output signal is reduced.

- Its bandwidth increases

Copyright reserved

|     |        | more resources like this on ECOLEBOOKS.COMology: Digital9DBE/November 2021NSC – Marking Guidelines                                                                                    |                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 4.2 | 4.2.1  | It stores the information it last received <th>(2)</th>                                                                                                                               | (2)                |

|     | 4.2.2  | + 5 V✓ to (+15 V or +18 V). ✓                                                                                                                                                         | (2)                |

|     | 4.2.3  | The three 5 k $\Omega$ resistors divide the supply voltage $\checkmark$ into three equal values that are used by the two comparators. $\checkmark$                                    | (2)                |

|     | 4.2.4  | <ul> <li>Astable Mode </li> <li>Monostable </li> <li>Bistable</li> </ul>                                                                                                              | (2)                |

|     | 4.2.5  | The pin monitors the voltage at which a 555 IC will trigger. $\checkmark$ When the threshold voltage ( $^{2}_{3}$ V <sub>cc</sub> ) is exceeded, the IC will reset. $\checkmark$      | (2)                |

| 4.3 | wavefo | I1 Op-amp amplifies the difference between two inputs, ✓ therefore<br>rms with equal amplitudes at the inputs ✓ would cancel each other<br>an output of zero (common mode rejection). | (3)<br><b>[20]</b> |

### **QUESTION 5: DIGITAL AND SEQUENTIAL DEVICES**

5.1 The cathodes of all eight LED's are internally connected ✓ to a 0 V or common ground. ✓

5.2

(5)

(3)

(2)

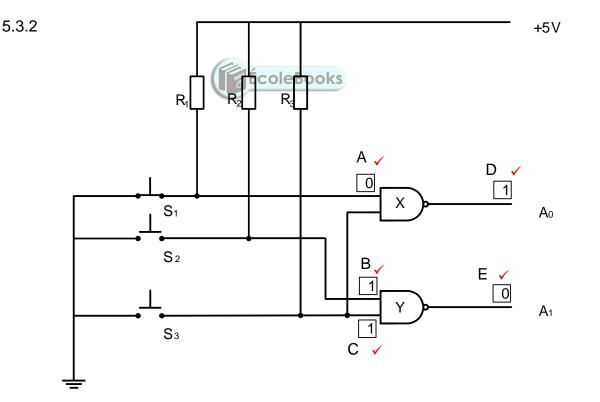

5.3 5.3.1 An encoder accepts the input data ✓ in a decimal format ✓ and converts it to binary format ✓

(5)

| Download more :               | resources | like            | this      | on | ECOLEBOOKS.COM    |

|-------------------------------|-----------|-----------------|-----------|----|-------------------|

| Electrical Technology: Digita |           | 11<br>– Marking | Guideline | S  | DBE/November 2021 |

|                               |           |                 |           |    |                   |

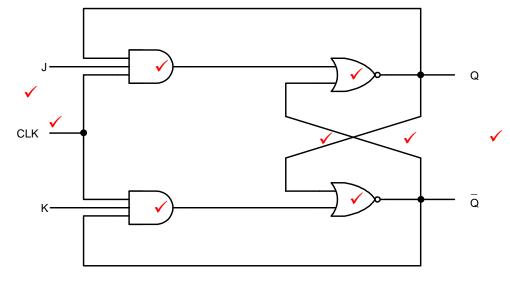

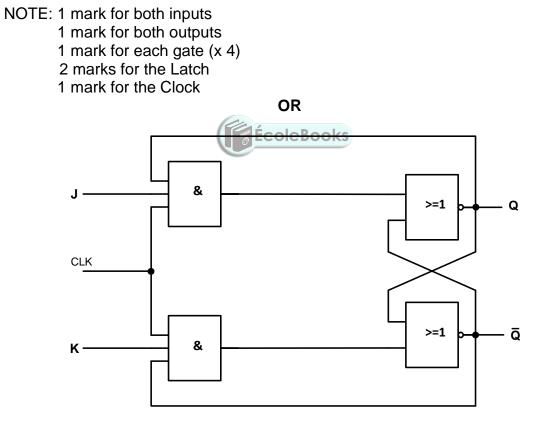

| 5.4                           |           |                 |           |    |                   |

(9)

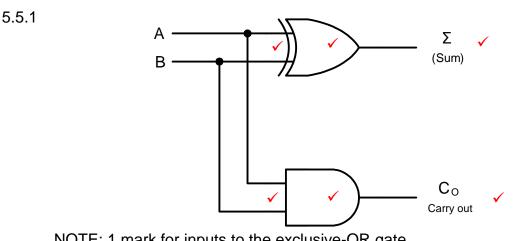

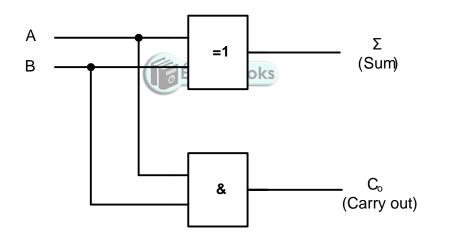

## NOTE: 1 mark for inputs to the exclusive-OR gate 1 mark for inputs to the AND gate 1 mark for Sum ( $\Sigma$ )

1 mark for  $C_o$

1 mark for each gate (x 2)

OR

#### 5.5.2

| INPUTS |   | OUTPUTS |     |  |

|--------|---|---------|-----|--|

| A      | В | Σ       | Co  |  |

| 0      | 0 | 0       | 0   |  |

| 0      | 1 | 1 🗸     | 0   |  |

| 1      | 0 | 1       | 0 🗸 |  |

| 1      | 1 | 0 🗸     | 1   |  |

(3)

(2)

(2)

(6)

- 5.6 Frequency divider ✓

Decade Counter ✓

Binary Coded decimal (BCD) counter

- 5.7 A full sequence counter is a counter that runs to its maximum count. ✓ A truncated counter is a counter that is modified to stop its count before reaching its maximum count. ✓

Please turn over

DOWNLOAD MORE RESOURCES LIKE THIS ON ECOLEBOOKS.COM

Electrical Technology: Digital

13 NSC – Marking Guidelines DBE/November 2021

- 5.8 Positive edge triggering is when the circuit reacts ✓ to the positive (or leading) edge ✓ of the pulse which rises from 0 to 1.

- (2)

(8)

- 5.9 On beginning a count, FF<sub>0</sub> and FF<sub>2</sub> outputs feed the input of the NAND gate with a low '0'  $\checkmark$

- this means that the gate's output will be high '1' and it is this high '1' that enables the counter to begin operating as a normal 'up' counter. ✓

- It continues with the up-count until reaching the binary output number 101₂ (decimal 5). ✓

- At this point both Q<sub>0</sub> and Q<sub>2</sub> outputs are high '1' which feed the input of the NAND gate, ✓ causing its output to fall to low '0'. ✓

- This low '0' immediately disables the first flip-flop FF<sub>0</sub>  $\checkmark$

- preventing it from responding to any further input clock pulses. ✓

- This effectively stops the counter, placing it on hold in the 101<sub>2</sub> (5<sub>10</sub>) state until a further reset signal is introduced. ✓

**NOTE:** The circuit as taken from the textbook will not operate correctly and the answer given in this marking guideline will be accepted as it is in the official textbook.

Learners who indicated that the counter would jump from five  $(101_2)$  to seven  $(111_2)$  will be credited.

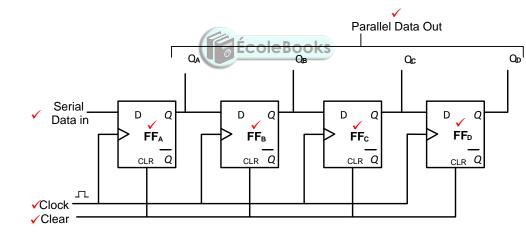

- NOTE: 1 mark for Serial data input

- 1 mark for Parallel data output

- 1 mark for each labelled flip-flop (x 4)

- 1 mark for the Clear

- 1 mark for the Clock

(8) **[55]**

5.10

#### 14 NSC – Marking Guidelines

(3)

(1)

(1)

(1)

# NSC – Marking Guiden

#### **QUESTION 6: MICROCONTROLLERS**

6.1 A microcontroller is a single chip ✓ (integrated circuit) that performs a dedicated task ✓ as an independent device. ✓

#### OR

A microcontroller is an independent device, a computer on a chip that can perform a limited range of functions without needing to rely on other chips or devices.

- 6.2 The CPU sends an address to the RAM to request data. ✓

- The CPU will receive the data once the enable wire is activated.

- The CPU will then process the data. ✓

- The CPU will send another address to the RAM telling it where to store the data. ✓

- The RAM will only receive the processed data when the enable wire is activated to be stored again. (4)

- 6.3 6.3.1 Logic 1 between -3 V and -25 V ✓ Logic 0 between +3 V and +25 V ✓ (2)

- 6.3.2 Applied in low-data-rate short range applications such as; printers, ✓ modems, ✓ data projectors, CNC machine tools (2)

- 6.4 6.4.1 (a) CPU ✓ (1) (b) Memory ✓ (1)

- 6.4.2 (a) Address bus ✓ (1)

- (b) Data bus 🗸

- 6.4.3 The purpose of the control bus is to issue control instructions ✓ to both memory ✓ and input/output ports. ✓ (3)

- 6.5 6.5.1 (a) Transmitter (Sender) / Tx 🗸

- (b) Receiver / Rx ✓

- 6.5.2 Data is sent as one long stream of bits or, as a block of data ✓ with each bit following the next. ✓

- At the receiving end, the bits are counted and reconstructed into bytes. ✓

- For this to be successful it is essential that strict timing ✓ is kept between the transmitter and receiver units.

- This is achieved by synchronising both the sender and receiver with a common clock pulse. ✓

- This method's accuracy depends on the receiver being able to keep an accurate count of the bits as they arrive. ✓

(6)

| Download more                | resources | like | this | on | ECOLEBOOKS.COM    |  |

|------------------------------|-----------|------|------|----|-------------------|--|

| Electrical Technology: Digit | al        | 15   |      |    | DBE/November 2021 |  |

| NSC – Marking Guidelines     |           |      |      |    |                   |  |

- 6.6 6.6.1 A set of rules and regulations that allow two electronic devices ✓ to exchange data and information between themselves. ✓

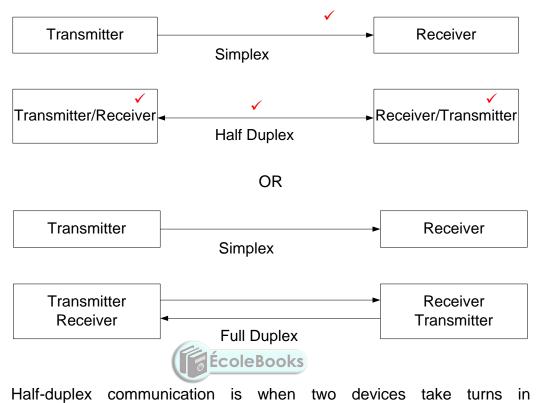

- 6.6.2

- 6.6.3 Half-duplex communication is when two devices take turns in communicating, one after the other. ✓

Full-duplex communication is when two devices can both transmit and receive at the same time. ✓

- 6.7 6.7.1 A program is a sequence of instructions ✓ that tell a computer (PIC) how to do a task. ✓

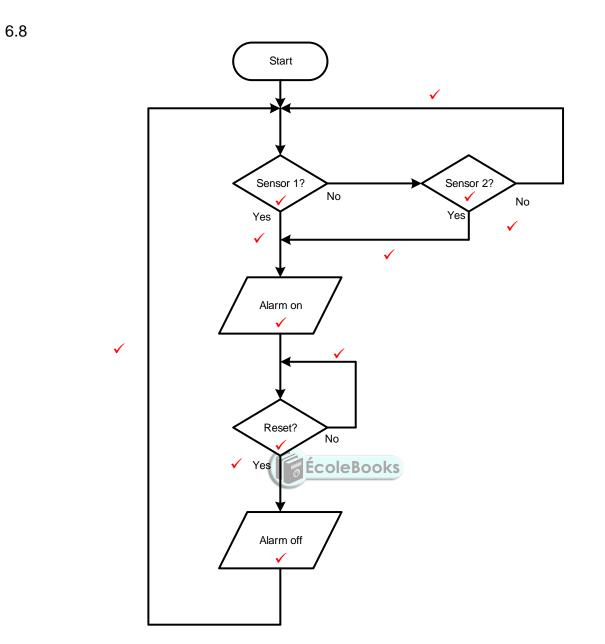

- 6.7.2 A flow diagram is a visual representation of steps and decisions ✓ needed to perform and complete a process. ✓

(2)

(4)

(2)

(2)

(2)

NOTE: 1 mark for each correct symbol (x 5) 1 mark for each correct placement of Yes/No (x 3) 1 mark for each correct flow line (x 4)

(12)

[50]

TOTAL: 200

Copyright reserved